Scott Young's Email & Phone Number

Hardware Design Engineer at Apple

Scott Young Email Addresses

Scott Young Phone Numbers

Scott Young's Work Experience

PRO Unlimited / Apple

Contract Engineer

November 2017 to January 2019

Terabit Radios Inc

VP of Product Development/System Architect

January 2015 to June 2016

Rode Microphones

Wireless Product Architect

May 2013 to December 2014

Mojokitchenz Inc.

Chief Technical Officer/Founder

April 2011 to May 2013

Brace Audio

Chief Technical Officer/Founding partner

February 2006 to April 2011

C-CUBE microsystems/DIVICOM Inc

Hardware Design Engineer

February 1995 to July 1998

Show more

Show less

Frequently Asked Questions about Scott Young

What is Scott Young email address?

Email Scott Young at [email protected] and [email protected]. This email is the most updated Scott Young's email found in 2024.

What is Scott Young phone number?

Scott Young phone number is +1.8312781902 and +1.8313451346.

How to contact Scott Young?

To contact Scott Young send an email to [email protected] or [email protected]. If you want to call Scott Young try calling on +1.8312781902 and +1.8313451346.

What company does Scott Young work for?

Scott Young works for Apple

What is Scott Young's role at Apple?

Scott Young is Hardware Design Engineer ICT5

What industry does Scott Young work in?

Scott Young works in the Telecommunications industry.

Scott Young's Professional Skills Radar Chart

Based on our findings, Scott Young is ...

What's on Scott Young's mind?

Based on our findings, Scott Young is ...

Scott Young's Estimated Salary Range

Scott Young Email Addresses

Scott Young Phone Numbers

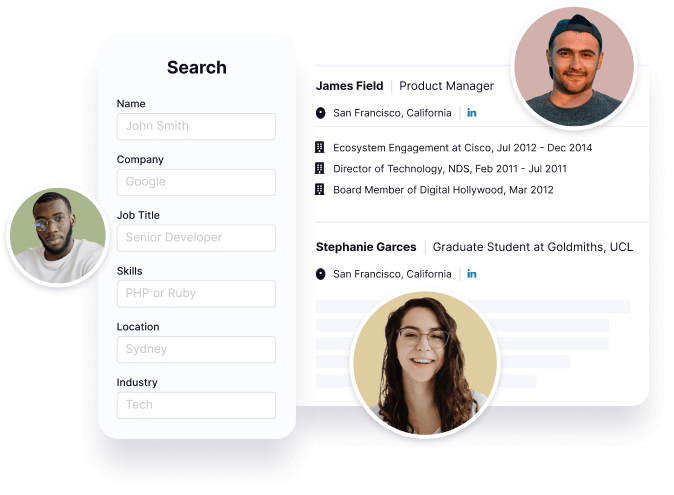

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Scott Young's Personality Type

Introversion (I), Intuition (N), Thinking (T), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Scott Young's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 91% chance that Scott Young is seeking for new opportunities

Top Searched People

Actress

Model and showgirl

Actor ‧ Thomas Gibson's ex-wife

Actor

Chief financial officer of Disney

Scott Young's Social Media Links

/in/scott-young-a43995 www.terabitradios.com