Richard Johnson's Email & Phone Number

Group Managing Director at Beadles Group Limited

Richard Johnson Email Addresses

Richard Johnson Phone Numbers

Richard Johnson's Education

Medway College of Technology

Show more

Show less

Frequently Asked Questions about Richard Johnson

What company does Richard Johnson work for?

Richard Johnson works for Beadles Group Limited

What is Richard Johnson's role at Beadles Group Limited?

Richard Johnson is Group Managing Director

What is Richard Johnson's personal email address?

Richard Johnson's personal email address is ri****[email protected]

What is Richard Johnson's business email address?

Richard Johnson's business email address is r****[email protected]

What is Richard Johnson's Phone Number?

Richard Johnson's phone +44 ** **** *200

What industry does Richard Johnson work in?

Richard Johnson works in the Automotive industry.

Richard Johnson's Professional Skills Radar Chart

Based on our findings, Richard Johnson is ...

What's on Richard Johnson's mind?

Based on our findings, Richard Johnson is ...

Richard Johnson's Estimated Salary Range

Richard Johnson Email Addresses

Richard Johnson Phone Numbers

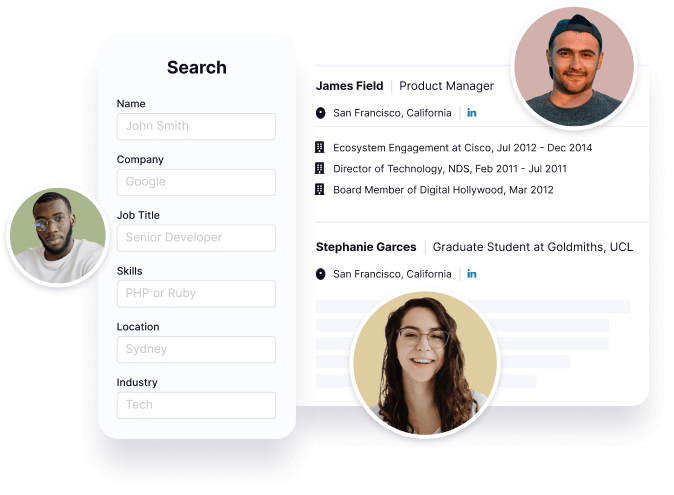

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Richard Johnson's Personality Type

Extraversion (E), Intuition (N), Feeling (F), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Richard Johnson's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 74% chance that Richard Johnson is seeking for new opportunities

Top Searched People

Actress

American YouTuber

Internet personality

American swimmer and athlete

American writer and television producer

Richard Johnson's Social Media Links

/in/richard-johnson-8638642 www.beadlesa.co.uk