Etai Mizrahi's Email & Phone Number

Co-Founder @ Secoda (YC S21) - We're hiring

Etai Mizrahi Email Addresses

Etai Mizrahi's Work Experience

Secoda (YC S21)

Co-Founder

March 2021 to Present

Secoda

Co-Founder

February 2021 to Present

Fushimi Productions

Founder

October 2015 to Present

Startup Laurier

VP Events & Competitons

April 2016 to Present

Gymnatik

Chief Marketing Officer

June 2016 to Present

Correly (Aquired by Acadium)

Co-Founder

July 2017 to September 2019

Generation Ventures

Venture Capital Analyst

January 2018 to April 2018

Advisor, Disruptive Technologies Unit

May 2017 to August 2017

Planitar

Consultant

September 2015 to April 2016

Striive

Co-Founder

Show more

Show less

Etai Mizrahi's Education

Lazaridis School of Business & Economics at Wilfrid Laurier University

January 2015 to January 2019

Waterloo Collegiate Institute (WCI)

January 2010 to January 2015

Y Combinator

Lazaridis School of Business & Economics at Wilfrid Laurier University

January 2015 to January 2019

Lazaridis School of Business & Economics at Wilfrid Laurier University

January 2015 to January 2019

Show more

Show less

Frequently Asked Questions about Etai Mizrahi

What is Etai Mizrahi email address?

Email Etai Mizrahi at [email protected]. This email is the most updated Etai Mizrahi's email found in 2024.

How to contact Etai Mizrahi?

To contact Etai Mizrahi send an email to [email protected].

What company does Etai Mizrahi work for?

Etai Mizrahi works for Secoda

What is Etai Mizrahi's role at Secoda?

Etai Mizrahi is Co-Founder

What is Etai Mizrahi's Phone Number?

Etai Mizrahi's phone (416) ***-*410

What industry does Etai Mizrahi work in?

Etai Mizrahi works in the Computer Software industry.

Etai Mizrahi Email Addresses

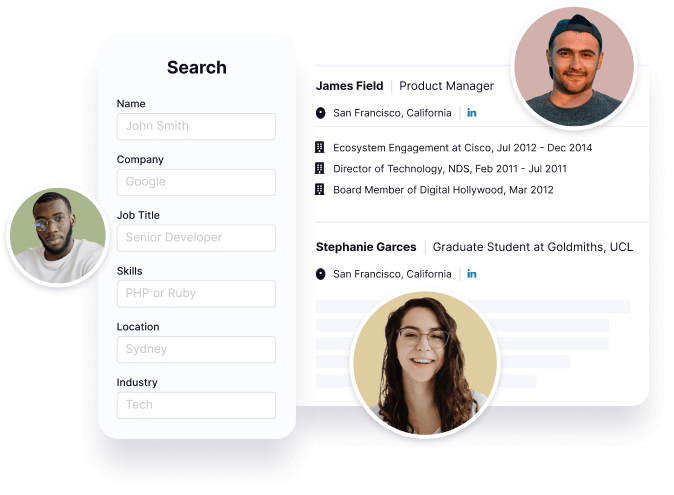

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Etai Mizrahi's Personality Type

Extraversion (E), Intuition (N), Feeling (F), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Etai Mizrahi's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 70% chance that Etai Mizrahi is seeking for new opportunities

Etai Mizrahi's Social Media Links

/in/etai-mizrahi-07656aa1