Chris Wang's Email & Phone Number

Taiwanese actor and model

Chris Wang's Email Addresses

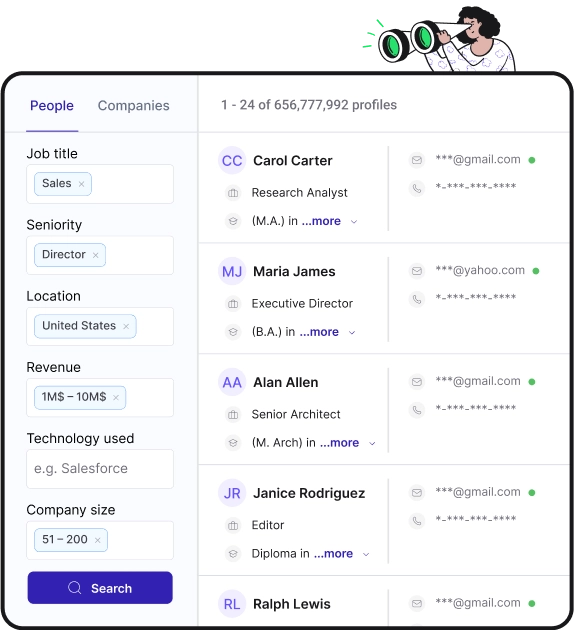

Find personal and work emails for over 300M professionals

Not the Chris Wang you were looking for? Continue your search below:About Chris Wang

📖 Summary

Chris Wang is a Taiwanese actor and model, best known for his work in a number of popular Taiwanese dramas and films. Born on June 9, 1982 in Taipei, Taiwan, Chris Wang's journey to becoming a successful actor and model began with his passion for the arts and a deep commitment to honing his craft.

Wang first gained recognition as a model, appearing in various fashion shows, commercials, and magazine spreads. His striking good looks and charismatic presence on the runway quickly caught the attention of casting agents and directors in the Taiwanese entertainment industry. This led to his transition from the world of fashion to that of film and television, where he found even greater success and acclaim.

One of Wang's most notable roles was in the hugely popular drama "In A Good Way," where he played the lead character, Liu Chuan. The series, which aired from 2013 to 2014, was a massive hit both in Taiwan and internationally, catapulting Wang to stardom and earning him a dedicated fan base. His portrayal of Liu Chuan, a charming and enigmatic university student, showcased his acting skills and solidified his status as a rising talent in the Taiwanese entertainment industry.

In addition to his work on the small screen, Wang has also appeared in several films, further showcasing his versatility and range as an actor. His roles in movies such as "Lovesick" and "Batman: The Dark Knight" have allowed him to explore different genres and characters, demonstrating his ability to take on diverse and challenging roles with ease.

Wang's success as an actor and model can be attributed not only to his talent, but also to his dedication and hard work. He is known for his professionalism on set, as well as his commitment to continuously improving his skills as an actor. His passion for his craft is evident in every role he takes on, and it has earned him the respect and admiration of his peers in the industry.

In addition to his work in front of the camera, Wang is also known for his philanthropy and humanitarian efforts. He has been involved in various charitable initiatives and projects aimed at helping those in need, utilizing his platform to raise awareness for important causes and make a positive impact in the world.

With his captivating on-screen presence, impressive acting chops, and commitment to using his fame for good, Chris Wang has solidified his status as one of Taiwan's most talented and beloved actors. His work continues to inspire and entertain audiences around the world, and his future in the entertainment industry looks as bright as ever.

Overall, Chris Wang is a multitalented individual who has achieved great success as both an actor and a model. His dedication to his craft, his philanthropy, and his ability to connect with audiences have made him a respected and beloved figure in the Taiwanese entertainment industry. Whether gracing the cover of a fashion magazine or mesmerizing viewers with his compelling performances on screen, Chris Wang continues to leave a lasting impression as a versatile and accomplished talent.

Frequently Asked Questions about Chris Wang

Who is Chris Wang's wife?

Wang dated and married his manager, Lin Yi-xian (林宜嫻), in 2015. They have one daughter, Wang Lei-zhen (王蕾榛), born on 9 April 2015, and a son who was born in June 2017.

How old is Chris Wang?

41 years (June 9, 1982)

Chris Wang's Email Addresses

People you may be

interested in

Film producer

American artist and musician

Musician

British actor

Canadian physician

Football wide receiver

American actor and writer

Italian comedian and film actor

American actress and model

American actress

American comedian

YouTuber