Danny Mclaughlin's Email & Phone Number

Business Development.

Danny Mclaughlin Email Addresses

Danny Mclaughlin's Work Experience

PERT AIR CONDITIONING LIMITED

Managing Director

October 2020 to Present

FM Systems UK

Group Managing Director

January 2021 to Present

Coolair

Sales Specialist

October 2021 to October 2021

York Appliances & HVAC

UK & Ireland Sales Manager York in-direct

October 2019 to October 2020

Iglu Cold Systems Ltd

General Manager (UK)

January 2013 to October 2019

Bespoke Design Consortium Ltd

Owner/MD

November 2018 to October 2019

Consort Refrigeration & Air Conditioning Ltd

Sales Director

October 2010 to July 2012

Mitsubishi Electric UK

Area Sales Development

January 2005 to October 2010

Sales Specialist

Show more

Show less

Danny Mclaughlin's Education

Girvan Academy

Show more

Show less

Frequently Asked Questions about Danny Mclaughlin

What is Danny Mclaughlin email address?

Email Danny Mclaughlin at [email protected]. This email is the most updated Danny Mclaughlin's email found in 2024.

How to contact Danny Mclaughlin?

To contact Danny Mclaughlin send an email to [email protected].

What company does Danny Mclaughlin work for?

Danny Mclaughlin works for PERT AIR CONDITIONING LIMITED

What is Danny Mclaughlin's role at PERT AIR CONDITIONING LIMITED?

Danny Mclaughlin is Managing Director

What is Danny Mclaughlin's Phone Number?

Danny Mclaughlin's phone +44 ** **** *282

What industry does Danny Mclaughlin work in?

Danny Mclaughlin works in the Business Supplies & Equipment industry.

Danny Mclaughlin Email Addresses

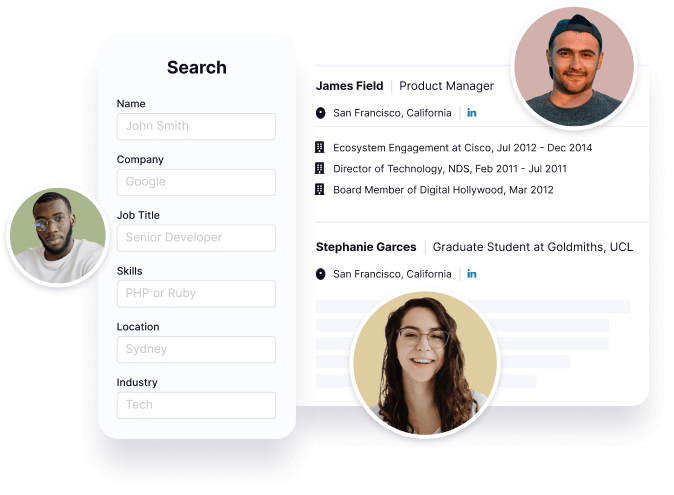

Find emails and phone numbers for 300M professionals.

Search by name, job titles, seniority, skills, location, company name, industry, company size, revenue, and other 20+ data points to reach the right people you need. Get triple-verified contact details in one-click.In a nutshell

Danny Mclaughlin's Personality Type

Extraversion (E), Intuition (N), Feeling (F), Judging (J)

Average Tenure

2 year(s), 0 month(s)

Danny Mclaughlin's Willingness to Change Jobs

Unlikely

Likely

Open to opportunity?

There's 74% chance that Danny Mclaughlin is seeking for new opportunities

Danny Mclaughlin's Social Media Links

/in/danny-mclaughlin-b09a9672